Silicon Pixel Detector

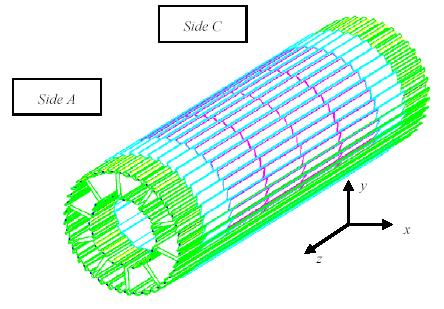

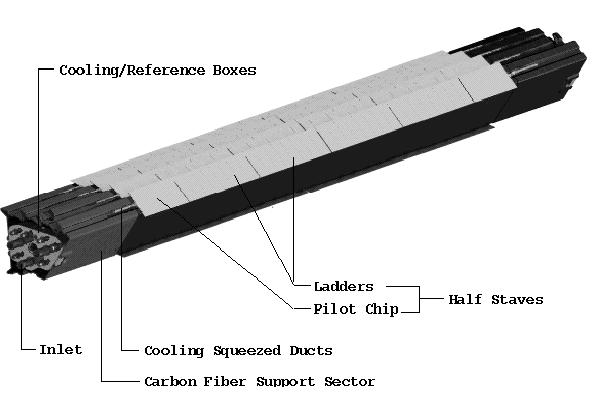

Silicon pixel detector (SPD) skģada się z dwóch cylindrycznych warstw o promieniach 3.9cm i 7.6 cm od ķrodka wiązki. Wygląd caģoķci jest pokazany na rys. 1. [7]

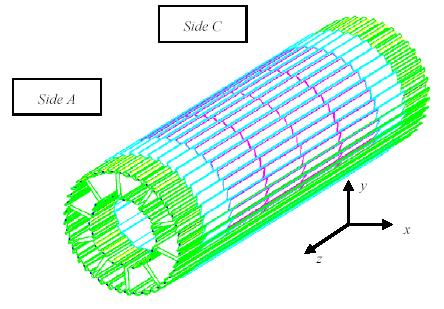

Rys.1 Wygląd caģoķci SPD [7] Rys.2 Zewnętrzny wygląd oraz przekrój SPD [5]

Lekka i

sztywna konstrukcja z wģókien węglowych rys.2 podtrzymuje zarówno warstwy detektorów,

jak i system chģodzenia oraz okablowanie. Podstawową częķcią detektora jest

sektor. Caģy SPD skģada się z 10 sektorów rys. 3

Although the sector is a rigid object, in the numbering and naming conventions

it is subdivided into two half-sector corresponding to detector sides A and

C. This segmentation is important for the online conventions as both sides

of one sector are readout separately.

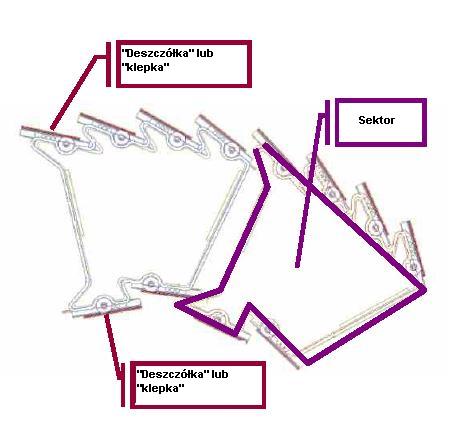

Rys. 3Prototyp pojedynczej deszczuģki detektora[5] Rys.4 Rozmieszczenie dwóch sektorów w przestrzeni [7]

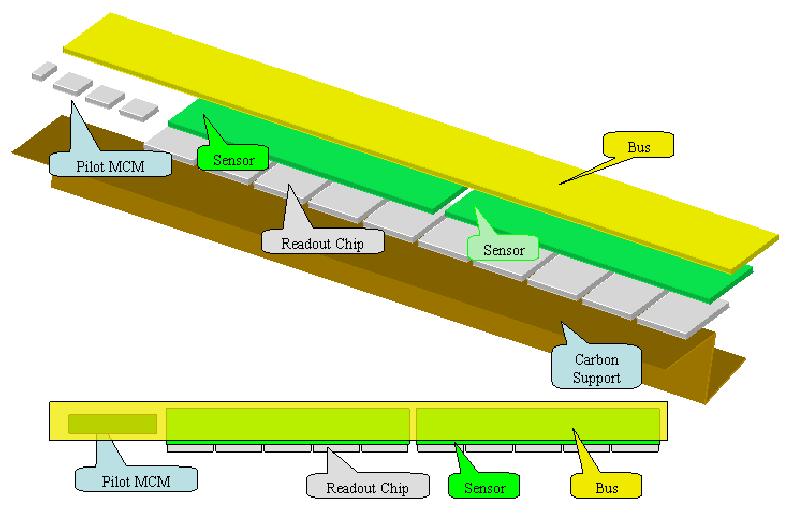

Podstawowym elementem stukturalnym SPD jest "deszczóģka"(klepka) skģadająca się z dwóch matryc czujników pixelowych i doģączonej elektroniki sczytującej. Aktywna powierzchnia caģkowita kaŋdej matrycy wynosi 12.8*69.6 mm2 i jest obsģugiwana przez 5 chipów odczytujących. Odczyt jest kontrolowany przez multichip module(MCM) umieszczony na skraju kaŋdej deszczóģki. Wielowarstwowa magistrala ģączy wszystkie elektroniczne elementy w jedną caģoķæ Rys.4

Rys. 5 Schemat deszczóģki, pokazane są podstawowe komponenty: chipy sczytująceALICE1, matryce czujników pixelowych, MCM, magistrale oraz konstrukcje podtrzymującą z wģókien węglowych. [7]

Pięæ ukģadów front-end ALICE1, kaŋdy zawierający elektronikę zczytującą z matrycy 256x32 komórek jest przyklejonych do drabinki za pomocą technologii flip-chip. W sumie na detektor SPD skģada się 60 "klepek" 240 drabinek i 9,8 miliona komórek. Dziesięæ takich sektorów jest zmontowane razem dookoģa rurki tworząc zamkniętą "beczkę".

Deszczóģka jest waŋnym obiektem z punktu widzenia caģego systemu, wszystkie chipy naleŋące do deszczóģki mają poģączone wyjķcia dostarczając w sumie pojedynczy blok surowych danych do obróbki, jednak moŋna uzyskaæ dostęp do kaŋdego chipu oddzielnie, deszczóģka jest takŋe podstawowym moduģem dla programów monitorujących i sterujących.

Sercem systemu jest chip ALICE1 przyklejony w technologii flip-chip do krzemowego detektora. Kaŋdy chip skģada sie z 8192 kanaģów odczytujących zorganizowanych w matryce 256x32. Kaŋdy kanaģ zawiera 5 jednobitowych rejestrów kontrolujących.

| Dwie cylindryczne warstwy | Ri= 39mm, Ro = 76mm |

| Wymiary komórek | 50mm (r f) x 425mm (z) |

| Elektronika sczytująca | CMOS6 0.25mm standard process on 8 wafers, rad-hard design |

| Pixel ASIC[8] gruboķæ (target) | <150 um (wafers thinned after bump deposition) |

| Si sensor ladder thickness | <200um |

| Flip-chip | bumps/indium bumps |

| Pixel bus | aluminium-polyimide flex |

| Cooling | water/C6F14/[C3F8 (evaporative)] |

| Material budget (each layer) | 0.9% X0 (Si~ 0.37, cooling ~0.3, bus ~0.17, support ~0.1) |

| Caģkowita powierzchnia Si | 0.24 m2 |

| Objętoķæ w caģym ALICE | < 2% |

Tabela 1 Parametry konstrukcyjne [5]

Rys. 3Cztery klepki oparte na wspornikach z wģokien węglowych zewnętrzenej warstwy SPD. Sektor jest wyposaŋony w sprasowane kanaģy chģodzące, biegnące pod klepkami. Czynnikiem chģodzącym jest fluorocarbon.